编者按:MLSys 大会全称为“Conference on Machine Learning and Systems”,由 Jeff Dean、Michael Jordan 和 Yann LeCun 等计算机系统和人工智能领域的全球顶尖科学家于2019年发起。2021年的 MLSys 大会共收到221篇投稿,52篇被录用,其中微软有四篇入选。本文将为大家介绍来自微软亚洲研究院的一项工作:通过分析深度学习算法设计空间在移动端侧推理平台的行为特性,以设计针对不同平台的高效深度学习模型。

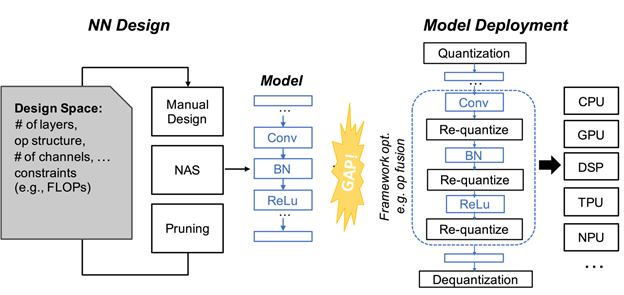

传统上,深度学习算法设计和部署平台的开发是相对独立的。算法设计科学家往往侧重于模型精度,而模型运行效率则是通过在设计中加入计算量的限制来进行保证。

图1:深度学习算法设计和模型部署平台的开发是相对独立的。

但近日,微软亚洲研究院异构计算组的研究员们在一篇题为“To Bridge Neural Network Design and Real-World Performance: A Behavior Study for Neural Networks”的论文中提出:仅仅用计算量来限制并不能保证实际部署的运行效率。

论文链接:

https://proceedings.mlsys.org/paper/2021/hash/02522a2b2726fb0a03bb19f2d8d9524d-Abstract.html

研究员们表示,一个典型的例子是 MobileNetV3 相较于 MobileNetV2 具有更少的计算量和更低的内存使用,因此在 ARM A76 CPU + TFLite 推理时,V3 比 V2 快25%;但出乎意料的是在 Intel Movidius VPU + OpenVINO 推理时,V3 却比 V2 慢75%。

目前,此篇论文已经被 MLSys 2021 (Conference on Machine Learning and Systems)大会收录,其主要研究内容是通过分析深度学习算法设计空间在移动端侧推理平台的行为特性,以设计针对不同平台的高效深度学习模型。

换句话说,研究员们在论文中指出,当前仅仅用计算或访存量作为高效模型设计的指标是不合理的。每个部署框架都有不同的特性,高效算法设计必须考虑目标平台的特性,才能取得最好的性能。

研究目标:评估深度学习算法的行为特性

让算法设计者理解目标平台的特性是非常困难的。因为算法和平台设计往往属于不同的研究领域,有很高的学习门槛。更重要的是,近年来部署平台的迭代速度越来越快,而且很多平台的软硬件都是闭源的,因此对于这些平台的特性更是无从得知。

基于此,微软亚洲研究院的研究员们提出了通过评估整个深度学习算法设计空间在目标平台上的行为特性来指导高效的算法设计。其目标是回答以下三个研究问题:

1. 算法设计空间中有哪些异常的行为特性?这里的异常特性是指:不同算法配置会导致计算或访存量增加或减少,但部署平台的推理延时没有相应地增加或减少。这些特性是在算法设计中要尤其注意利用或避免的。

2. 这些异常行为特性背后的原因是什么?

3. 这样的特性对高效的深度学习算法的设计有什么启示?

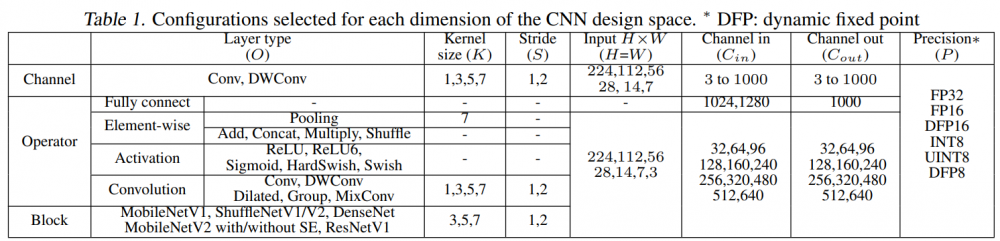

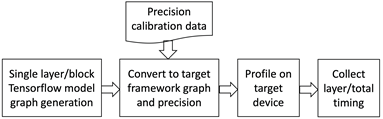

然而,由于每个算法的设计维度都有很多参数可选(本篇论文应用的是针对 ImageNet 的模型设计空间),整个算法空间轻易就能达到数十亿的数量级,评估所有参数会开销巨大,因此研究员们复用算法设计思路,每次仅调整和评估一个设计维度并固定其它维度以减小设计空间。此外,评估得到的每个维度行为特征可直接作为启发策略应用到算法设计中。研究员们还开发了一套全自动评估工具,流程如图2所示。

表1:本篇论文评估的所有算法设计维度(第一行),以及该维度下对应的配置

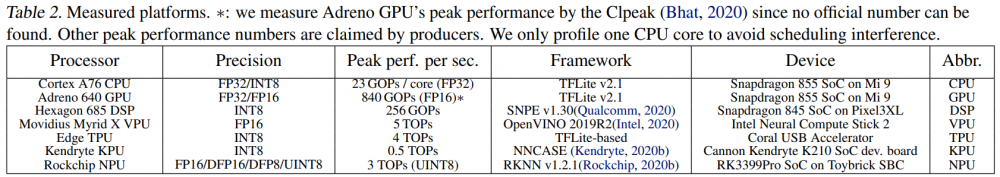

表2:评估中使用的七个部署平台

图2:本论文开发的全自动评估工具流程

最终,研究员们一共发现并总结了七条异常的行为特征可用于指导深度学习的算法设计。接下来,研究员们简要针对算法设计者常见的问题,介绍了该论文发现的行为特征以及背后的原因和启示。

研究发现:七个策略改进神经网络设计

(1)增加卷积通道数一定会增加推理延迟吗?

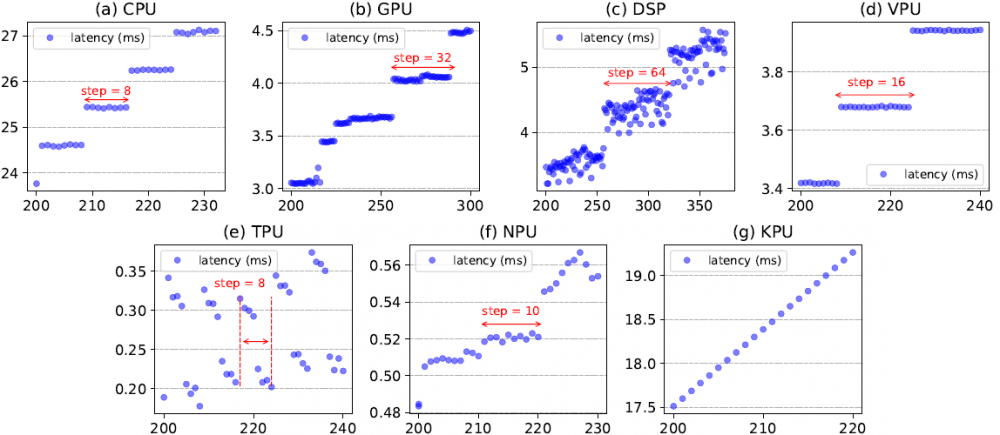

发现一:除 KPU 外,随着输出通道数的增加,卷积延时在推理平台上以阶梯式增加(如图3所示)。

图3:推理延迟(纵轴)随着输出通道数(横轴)的增加阶梯上升

原因:由底层硬件的数据级并行导致。以 CPU 为例,为使用 CPU 的数据级并行,即 SIMD 单指令多数据单元,推理框架会使用一个小数据块作为基本计算单位,比如 TFLite 使用(8,1)×(1,8)→(8,8)作为基本块,因此数据都要被填充成8的倍数,所以展示出如图3(a)中长度为8的阶梯行为。其他平台也是同样的原因。

启示:为了潜在的更高精度,在设计神经网络时建议保留每个延时台阶的最大通道数,跳过其它通道数。例如,如果在 MetaPruning (神经网络通道数自动剪枝)这篇论文中应用该启示的话,搜索空间能够从30^14降低到4^14。

(2)每个网络模块在不同平台上有相似的相对时延吗?

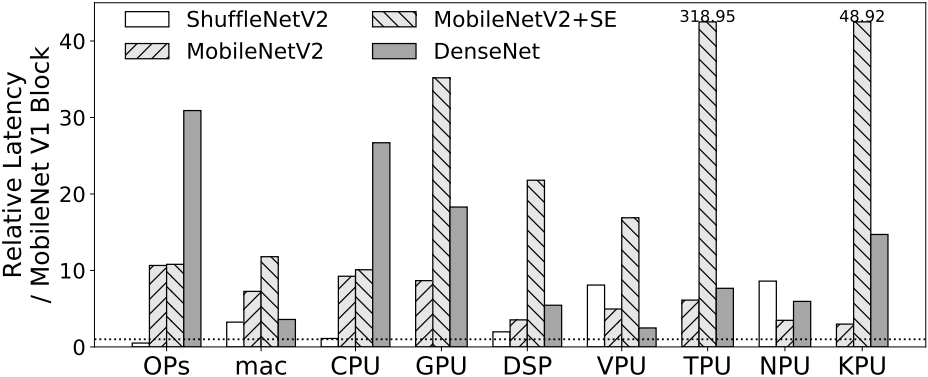

发现二:一个网络模块的相对延时在不同推理平台上差异很大。除了在 CPU 上,非卷积算子可能会极大地拖慢推理速度(如图4所示)。

图4:不同网络模块在不同平台上的相对时延差别很大(Ops 指计算量,mac 指访存量)

原因:一个原因是除了 CPU,其它推理平台上计算和访存带宽不匹配现象严重。在 CPU 上,模块相对时延和计算量相符,但在其它平台上,模块相对时延更体现了访存量的区别。另一个原因是,除 CPU 外其它推理平台对非卷积算子支持较弱。例如,图4展示了 SE(Squeeze and Excitation) 模块会显著增加模型在几个平台的延时。以 GPU 为例,SE 的 Pooling 缺少算子融合的支持,因此虽然 Pooling 只占了<5%的计算量,但却消耗了>70%的延时。

启示:算法设计空间的候选网络模块应该对每个推理平台进行定制。

(3)激活函数对时延影响很小吗?

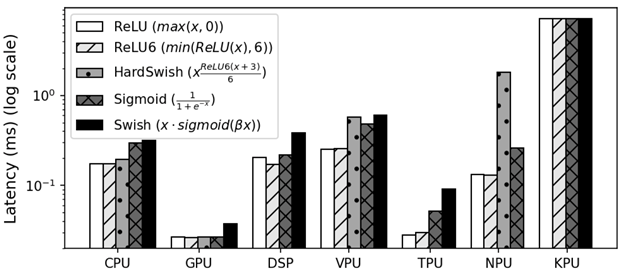

发现三:只有 ReLU 和 ReLU6 的延时在每个推理平台上可以忽略。HardSwish 只在 CPU 和 GPU 上可忽略。除了 KPU,Swish 激活函数在各个推理平台上都会显著增加推理延时(如图5)。

图5:不同激活函数在不同平台上时延不同(图中显示了 depthwise 卷积+激活函数的时延,因为激活函数通常和其它算子融合在一起)

原因:推理平台对新激活函数的算子融合支持较弱。例如,虽然 HardSwish 常常被认为是对部署友好的算子:和 Swish 相比,它移除了 Sigmoid 和指数函数以减少复杂计算。但是由于缺少算子融合支持,它在 NPU 上的推理延时甚至远远超过了 Swish。

启示:对每个推理平台的算法设计空间应考虑移除延时大的激活函数。

(4)用小卷积核可以极大减少时延吗?

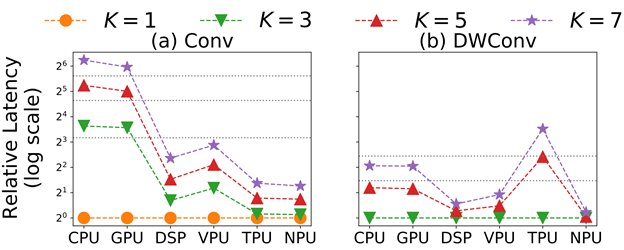

发现四:随着内核尺寸的增加,除了 CPU、GPU 和 Edge TPU 的 DWConv,Conv 和 DWConv 延时的增加都远小于计算量的增加。

原因:Conv 和 DWConv 在除 CPU 和 GPU 之外的平台上存储带宽都是受限的。当卷积核增大时,访存的增加要远小于计算量增加,因此延时增大不明显。

图6:卷积和 depthwise 卷积延时随卷积核大小(K)的变化

启示:在 NPU、DSP 和 VPU 上,应该使用更大尺寸的 DWConv 卷积核以得到模型精度的提升。同样,在 NPU、DSP 和 Edge TPU 上,则应该使用更大尺寸的卷积内核。

(5)使用低数据精度会在保证模型精度可接受的情况下相应地减少时延吗?

发现五:在 NPU 上应用 INT8 相较于 FP16 能获得11倍的加速比(除了 MobileNetV3 只有2.5的加速比)。然而,在 CPU 上,INT8 相较于 FP32 的加速比小于3.6。

原因:NPU 具有专门的 INT8 的计算单元,而不是像 CPU 和 GPU 一样在不同的运算精度之间共享计算单元。另外,在 CPU 上,INT8 重量化算子(requantization)对低数据重用率的算子代价很高。

启示:为了在 CPU 上获得最佳延时,每个算子应该选择合适的数据精度。

发现六:INT8 会在许多模型上显著降低推理精度。

原因:一些推理平台的 INT8 量化算法实现对某些算子不友好,从而导致精度降低。

启示:如果目标平台的数据精度是 INT8,那么在算法设计空间内应移除可能造成准确度损失的模块或算子。

(6)各个推理平台的横向比较是怎样的?

发现七:考虑到对神经网络模型的支持程度,特别是对新模型的支持程度,CPU 平台是最好的选择。考虑到延时和能耗,以及对基础的流行的神经网络模型的支持,Edge TPU 和 NPU 是最好的选择。

综上所述,研究员们提出了一个针对深度学习算法设计空间的数据集,通过在七种有代表性的边缘端侧推理平台上评估该数据集,发现了七个行为特征,并对每一个提出了相应的启发策略来改进高效的神经网络设计。案例研究表明,通过应用这些策略,通道剪枝和 NAS 的搜索空间可被大幅度减少。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。